#### 准教授 • 瀬戸 謙修

半導体・デジタル研究教育機構 半導体部門 応用分野

#### ▶ 研究内容

# 【技術紹介】

- 組み込みFPGA (eFPGA) 用EDAツール (論理合成、配置配線) 開発 デジタル回路を高効率・柔軟に実装できるeFPGA (SoC向けFPGA IP) は競争力のある半導体集積回路の設計上重要である。高性能な eFPGA設計に不可欠なEDAツールを開発している。

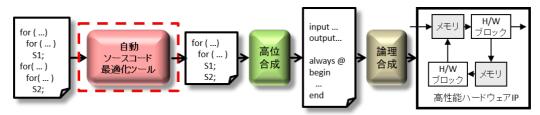

- 高位合成向けループ・メモリアクセス最適化、AIエッジアクセラレータ開発 Python、C言語等のアルゴリズムからハードウェアを自動生成する高位合成を用いることで、高性能、省エネルギー、小面積な集積回路 を自動生成できる。その際、ループ最適化やメモリ最適化を人手適用する必要があり、膨大な時間がかかるため、これら最適化を自動で 行うツールを開発した。この技術を使用して、短期間に高性能・省メモリなAIエッジアクセラレータを生成する技術を開発している。

```

1. for (i = 0; i < 42; i++)

for (i=0;i<=38;i++)

1. for (i=0;i<=38;i++)

for (j=0;j<=41;j++) {

for (j=0;j<=41;j++) {

y[i] = 0;

2.

2.

3. for (i = 0; i < 38; i++) {

3.

if (i \ge 1)

3.

if (i \ge 1)

4.

T[i] = 0;

4.

y[j]=y[j] + A[i-1][j] * T[i-1];

4.

y[j]=y[j] + A[i-1][j] * T[i-1];

for (j = 0; j < 42; j++)

if (i \le 37 \&\& j = 0)

5.

if (i <= 37 && j == 0)

T 1 W 0=0;

T[i] = T[i] + A[i][j] * x[j];

T[i]=0;

6.

for (j = 0; j < 42; j++)

if(i \le 37)

if (i \le 37) {

8

T[i]=T[i]+A[i][j]*x[j];

8.

if(j==0) \{ t_T_2 R=T_1 W_0; \}

y[j] = y[j] + A[i][j] * T[i];

8.

if (j > 0) { t_T_2_R=T_3_W_1; }

9.

if (i == 0)

9.

10.

y[j]=0; }

10.

T_3W_0=t_T_2R+A[i][j]*x[j];

11.

T[i]=T_3_W_0;

(a) 元コード

(b) ループ融合後のコード

12

13.

if (i == 0)

y[j]=0;

T_3_W_1=T_3_W_0; }

15.

(c)メモリアクセス最適化後のコード

```

(c) メモリアクセス取過10後のコート

# ▶ 提供できる技術

・eFPGA用EDAツール (論理合成、配置配線)・高位合成向 けコード最適化 (ループ最適化、メモリアクセス最適化)・ Pythonから高性能かつ省メモリ面積なエッジAI用アクセラ レータを自動生成する技術

# ▶ 特許

・特開2014-225201 ・特開2014-225200

#### ▶ 関連リンク

夢ナビ「未来の半導体チップ設計のためのEDA」

#### ▶ キーワード

半導体設計 FPGA EDA 高位合成 エッジAI ループ最適化 メモリ最適化 アクセラレータ 総合領域 計算基盤 計算機システム