●再構成可能な論理デバイスの実現

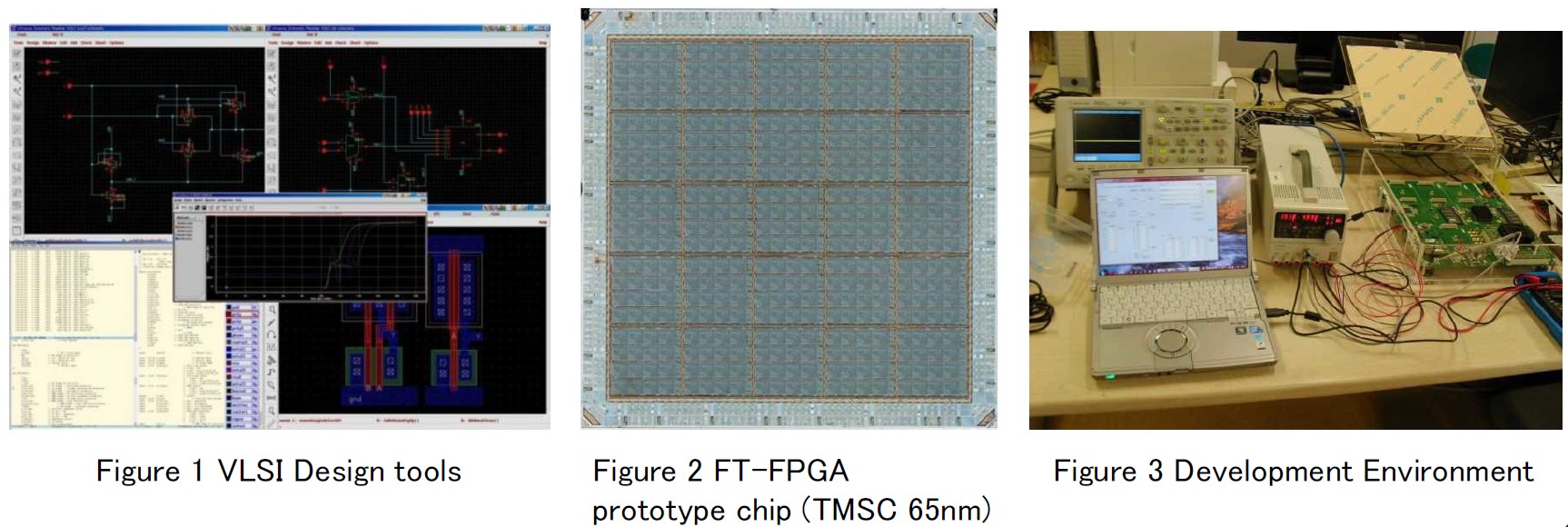

回路を動的に変更できるプログラマブルロジック・デバイス(FPGA)アーキテクチャの研究です.従来のプログラマブルデバイスと比べて信頼性が高く,高性能および低消費電力なデバイスを実現するために,耐故障FPGAアーキテクチャや3次元スタッキングFPGAアーキテクチャなどの新しい構造のデバイスを研究しています.

●FPGAコンピューティング

プログラマブルロジック・デバイス(FPGA)の応用として,コンピュータとネットワークのあらゆる場所で計算処理ができる分散型FPGAコンピューティングの研究を進めています.組込み処理では,FPGAはCPUより高い応答性と細粒度の演算能力,そして消費電力が少ないという利点があります.本研究では,ソフトウェアから自動的にFPGA用の回路に変換し実行する手法の開発を行っています.

●再帰再構成型AIチップ

プログラマブルロジック・デバイス(FPGA)技術を応用して,新しいニューロモルフィックデバイスの研究を進めています.低コスト,高ユーザビリティ,高速かつ超低消費電力なリコンフィギャラブルAIプラットフォームを構築することが目的です.