【技術紹介】

- 組み込みFPGA (eFPGA) 用EDAツール (論理合成、配置配線) 開発

デジタル回路を高効率・柔軟に実装できるeFPGA (SoC向けFPGA IP) は競争力のある半導体集積回路の設計上重要である。高性能なeFPGA設計に不可欠なEDAツールを開発している。

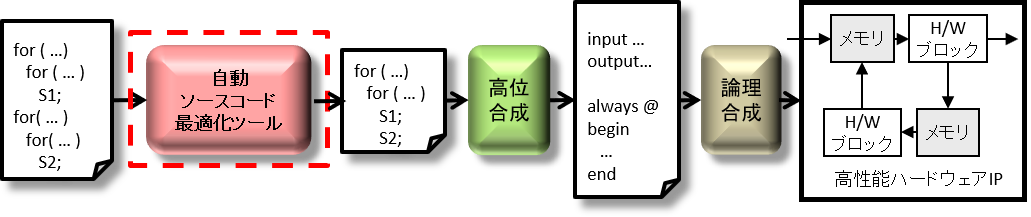

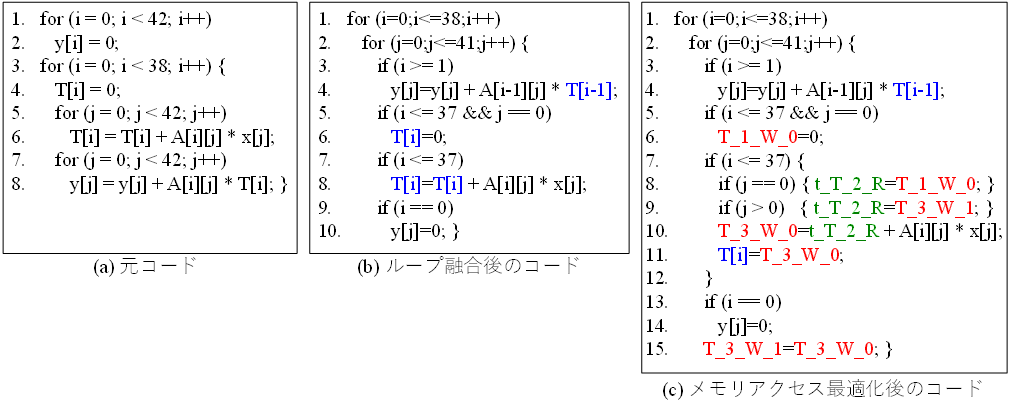

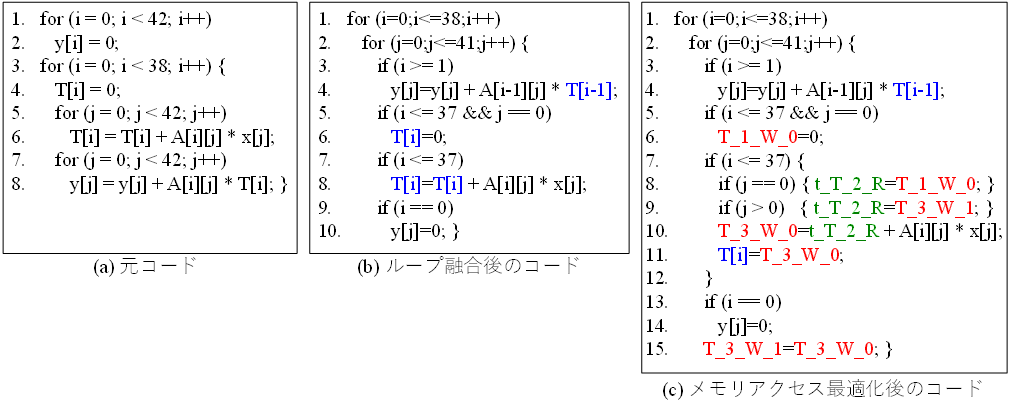

- 高位合成向けループ・メモリアクセス最適化、AIエッジアクセラレータ開発

Python、C言語等のアルゴリズムからハードウェアを自動生成する高位合成を用いることで、高性能、省エネルギー、小面積な集積回路を自動生成できる。その際、ループ最適化やメモリ最適化を人手適用する必要があり、膨大な時間がかかるため、これら最適化を自動で行うツールを開発した。この技術を使用して、短期間に高性能・省メモリなAIエッジアクセラレータを生成する技術を開発している。